DOCTORADO

Diseño de Circuitos Integrados VLSI

Tesis: Monitoreo Robusto del Envejecimiento y técnicas para mejorar el Rendimiento en Sistemas Digitales.

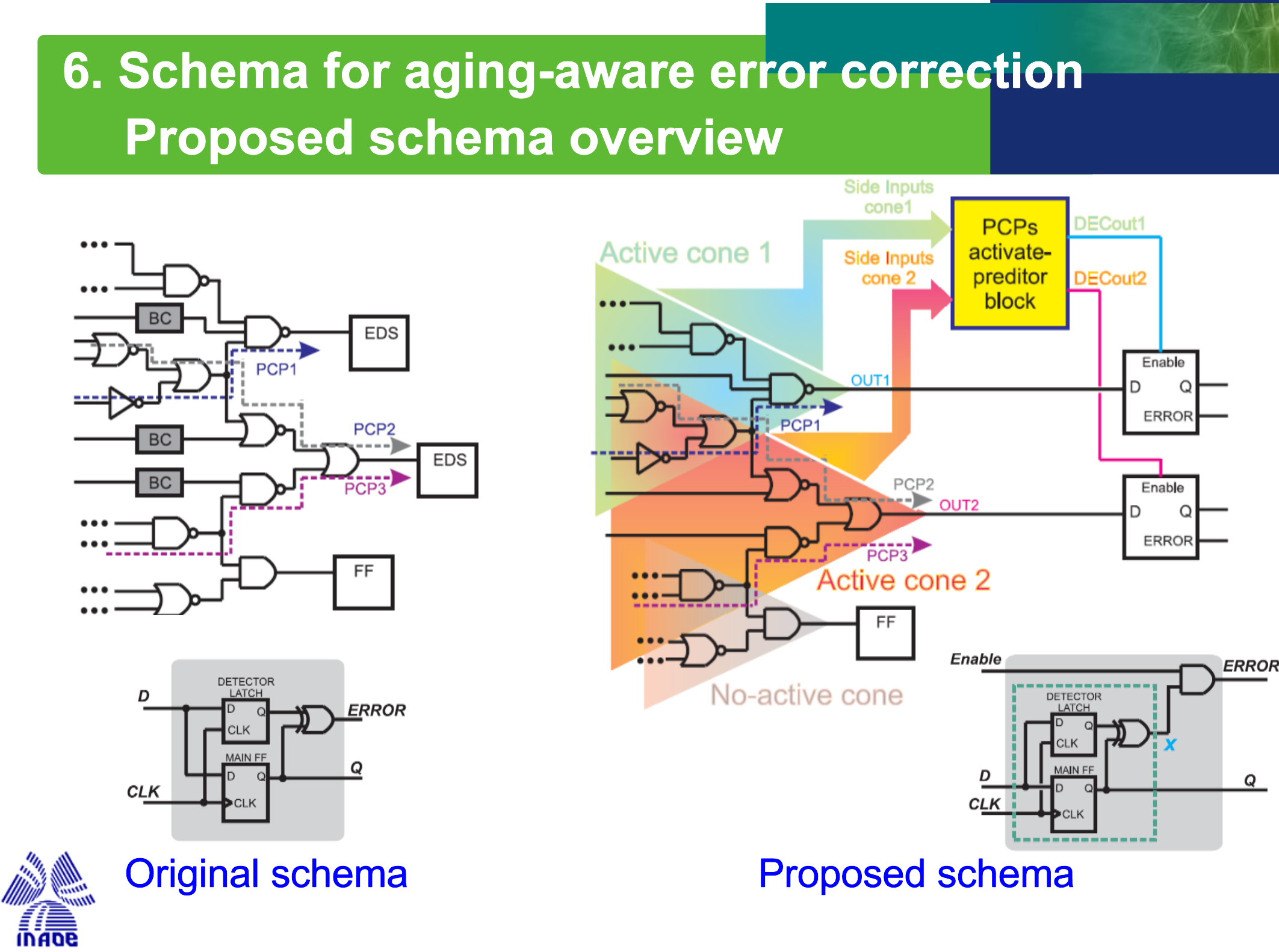

Para poder garantizar la operación confiable en tecnologías avanzadas un monitoreo del envejecimiento debe ser desarrollado dentro del chip usando sensores inter-construidos de envejecimiento. Las principales maneras para desarrollar dicho monitoreo del envejecimiento son clasificados en dos grupos: a) Predicción de errores y b) Corrección de errores. En esta tesis, serán propuestas varias metodologías y esquemas para realizar un monitoreo robusto del envejecimiento para la predicción y corrección de errores en circuitos integrados digitales nanométricos.

Conforme el escalamiento tecnológico ha progresado, los efectos de envejecimiento tales como el Negative Bias Temperature Instability (NBTI por sus siglas en inglés) han llegado a ser de suma importancia en tecnologías CMOS nanométricas. Por otro lado, el impacto de las variaciones paramétricas ha agravado aún más estos efectos. Las variaciones de Proceso, Voltaje, Temperartura y Envejecimiento (PVTA, por sus siglas en inglés) tienen un fuerte impacto en la fiabilidad y rendimiento en operación de los circuitos integrados. El envejecimineto por NBTI produce una degradación por rendimiento a medida que el tiempo de operación es mayor. El ritmo de dicha degradación depende de: a) las condiciones de operación que experimenten los circuitos tales como Voltaje, Temperatura y tiempo de estrés eléctrico de los transistores MOS y b) los parámetros tecnológicos estáticos definidos en el proceso de fabricación.

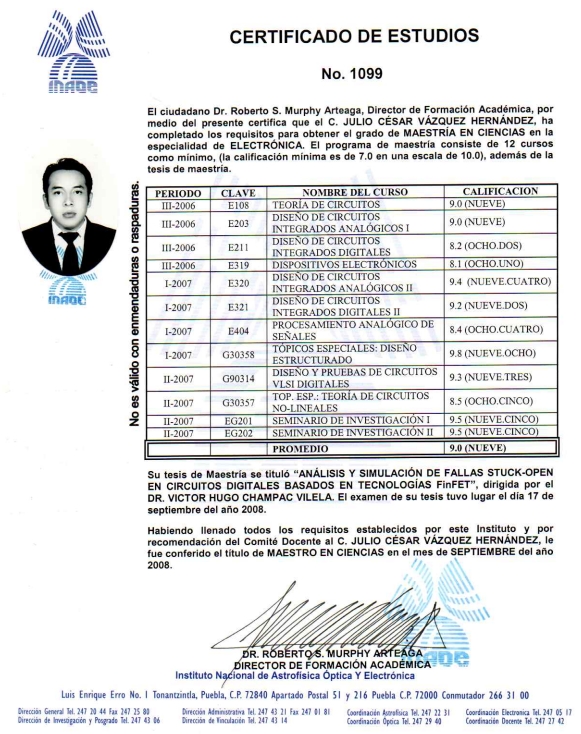

MAESTRIA

Diseño de Circuitos Integrados VLSI

Tesis: Análisis y simulación de fallas stuck-open en circuitos digitales basados en tecnologías FinFET

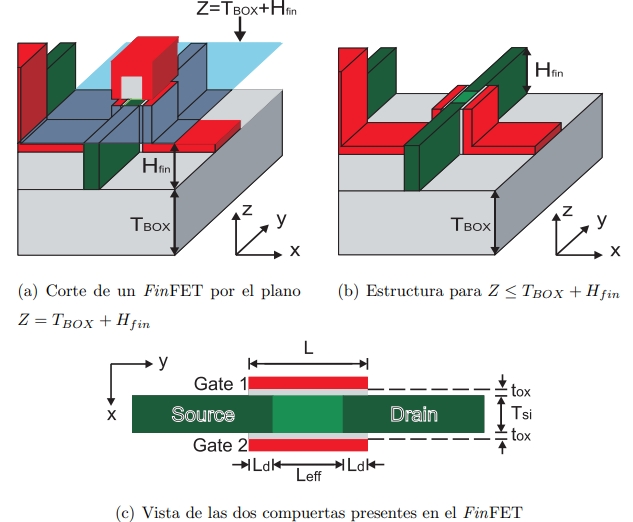

El diseño de circuitos integrados VLSI ha estado basado en el dispositivo MOSFET las últimas tres décadas. Sin embargo, el escalamiento del MOSFET en régimen manométrico presenta algunos efectos indeseables que degradan el rendimiento de este dispositivo. Una opción para seguir con el escalamiento tecnológico más allá de los 32nm es el empleo de nuevas estructuras, tal como los transistores de doble compuerta DGMOSFET, los cuales encuentran en el FinFET la manera más adecuada de fabricarlos. La International Technology Roadmap for Semiconductors (ITRS) reconoce la importancia de estos dispositivos en tecnologías futuras.

El FinFET pertenece a la familia de los dispositivos basados en tecnologías de Silicio sobre aislante. Es un dispositivo en forma de aleta, el cual está rodeado por un electrodo de compuerta formando dos canales propiamente alineados en las paredes verticales de dicha aleta. Fallas stuck-open han sido tradicionalmente reconocidas como de difícil detección en tecnologías debido principalmente a que se requiere una secuencia de vectores para su detección. Debido a que en tecnologías futuras; la densidad de dispositivos, así como el número de metales y el número de vías serán incrementados, se tendrá una probabilidad elevada de tener fallas stuck-open. El presente trabajo se enfoca al estudio de fallas stuck-open en compuertas CMOS estáticas basados en tecnologías FinFET. Por otra parte este trabajo pretende determinar de que manera las corrientes de fuga en los FinFETs afectan el comportamiento de las compuertas digitales bajo test.

INGENIERIA EN ELECTRÓNICA

La ingeniería fue cursada en el Instituto Tecnológico de Puebla. El título de ingeniero fue obtenido en automático por haber obtenido un promedio de 90/100 en las materias del programa de estudios. Algunos de los cursos más importantes que fueron acreditados en esta ingeniería fueron:

a) Sistemas Electrónicos Analógicos

b) Sistemas Electrónicos Digitales

c) Microcontroladores

d) Sistemas de Control

e) Instrumentación

f) PLCs

g) Robótica